Was ist NAND-Speicher?

NAND-Flash ist eine gängige Art von nichtflüchtigem Speicher (NVM). Im Gegensatz zu einem flüchtigen Speichertyp wie DRAM behält NAND-Flash Daten bei, wenn die Stromversorgung unterbrochen wird, ebenso wie viele Anwendungen.

Aber was ist NAND-Speicher und wie funktioniert er?

IN THIS GUIDE:

In diesem Leitfaden geht es um:

Obwohl der Schwerpunkt dieses Handbuchs auf NAND-Speicher liegt, werden wir den Speichertyp mehrmals mit NOR vergleichen.

Wofür steht NAND?

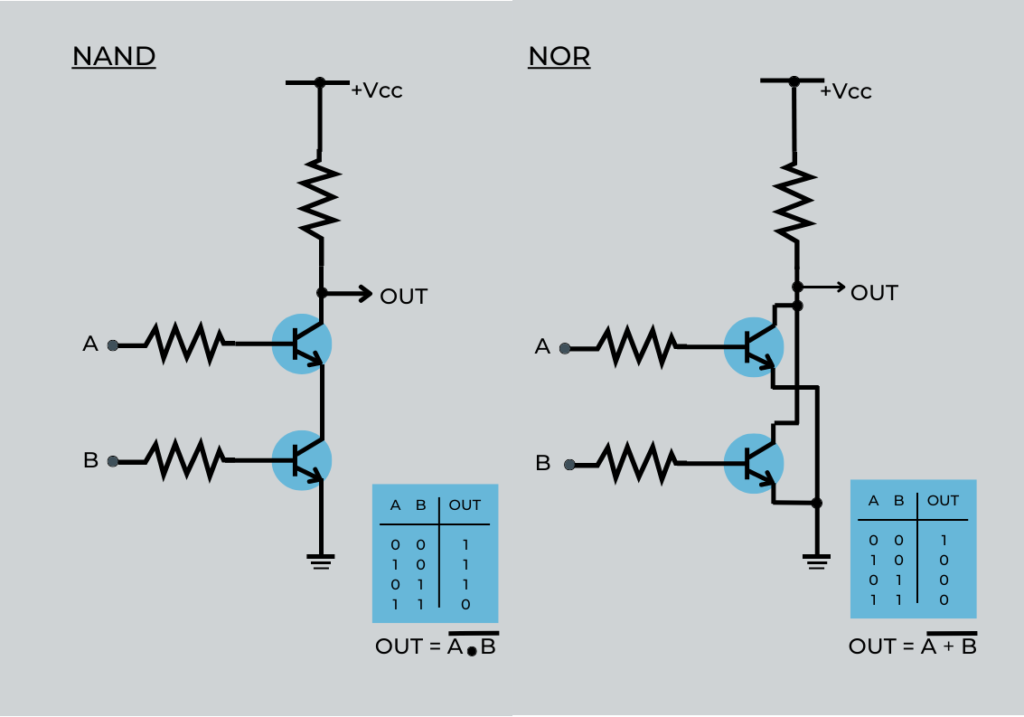

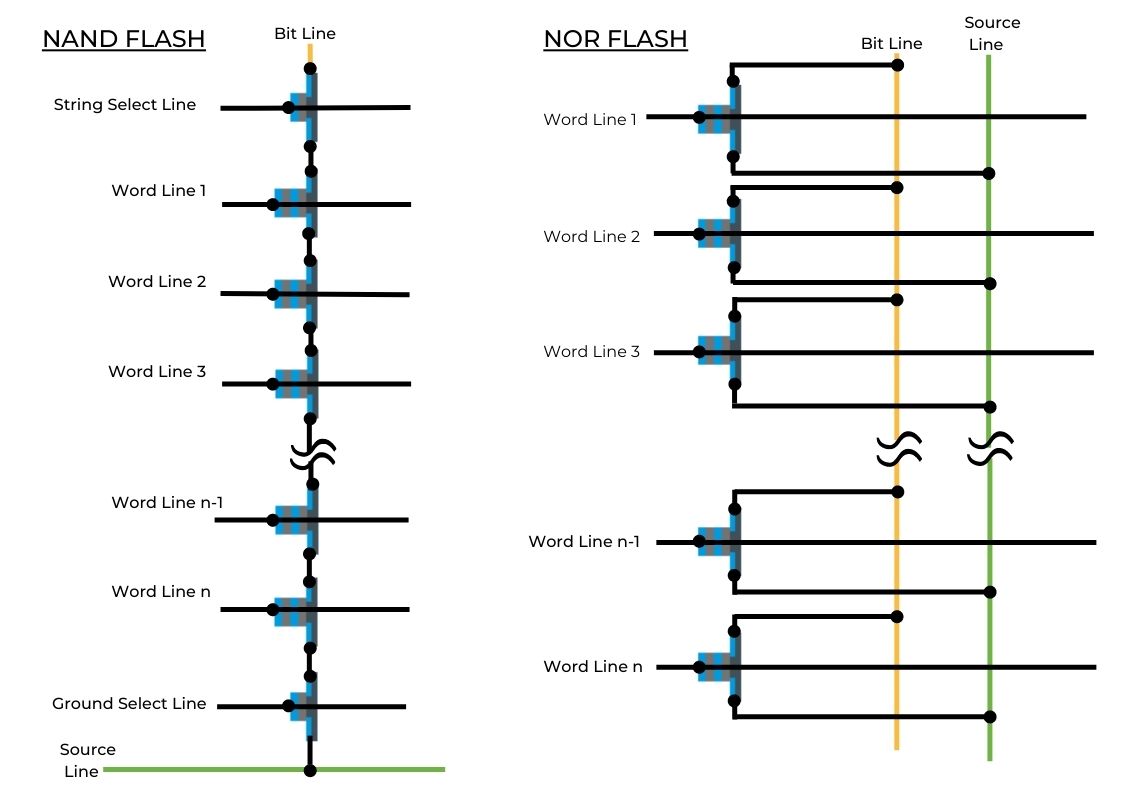

Der Begriff kommt vom logischen Ausdruck NOT AND, während sich NOR aus NOT und OR zusammensetzt. Beide Funktionen können in elektronischen Schaltungen mit Transistoren (die wie Schalter wirken) entweder in einer Reihenkonfiguration für NAND oder parallel für NOR erzeugt werden.

Siehe oben: Schaltkreise, Wahrheitstabellen und boolesche Ausdrücke für NAND (links) und NOR-Funktionen.

Obwohl sie nicht als herkömmliche Schalter im Speicher vorhanden sind, sind die jeweiligen Konfigurationen das Herzstück von NAND- und NOR-Flash. Jeder Transistor ist effektiv vorhanden, um Daten zu speichern, nämlich ein Bit oder mehr, worauf wir später zurückkommen. Außerdem neigen wir dazu, von NAND- und NOR-Speicherzellen und nicht Gattern (Gates) oder Transistoren zu sprechen.

Die NAND-Flash-Speicherzelle

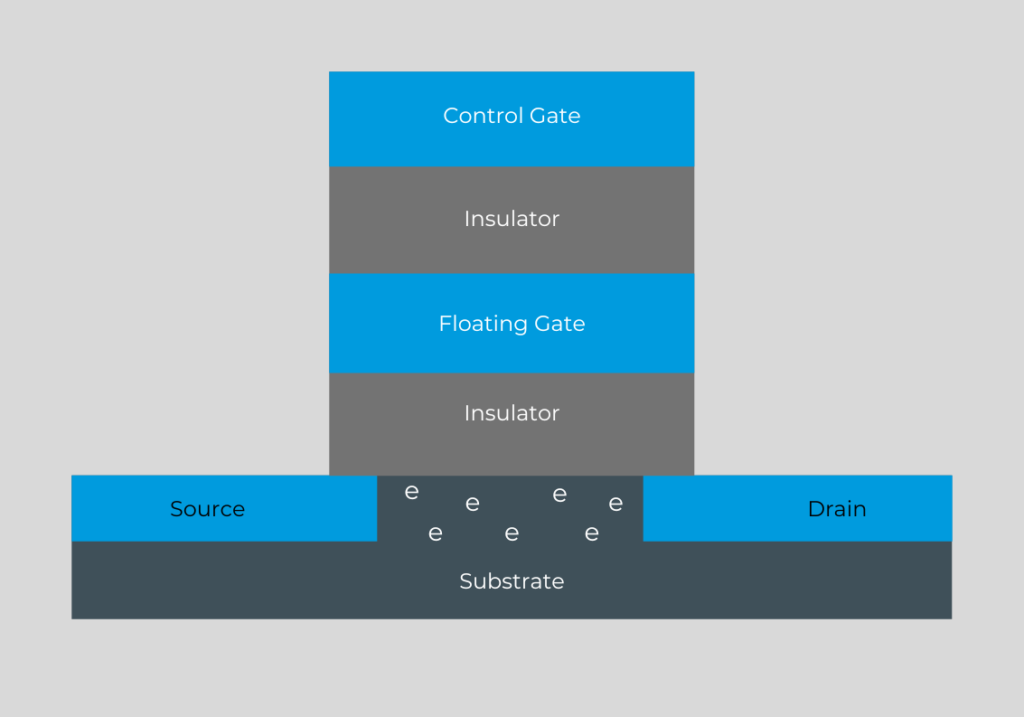

Eine Flash-Zelle ist effektiv ein N-Kanal-MOSFET-Transistor mit einem zusätzlichen Gatter – dem sogenannten Floating-Gate -, das zwischen zwei Isolatoren eingeklemmt ist. Wahrscheinlich das Gegenteil von dem, was Sie erwarten würden, denn wenn das Floating-Gate geladen ist, stellt es eine logische 0 dar und gilt als programmiert. Ungeladen wird die Zelle gelöscht und stellt eine logische 0 dar.

Lassen Sie uns auf das Schreiben, Lesen und Löschen von Daten eingehen

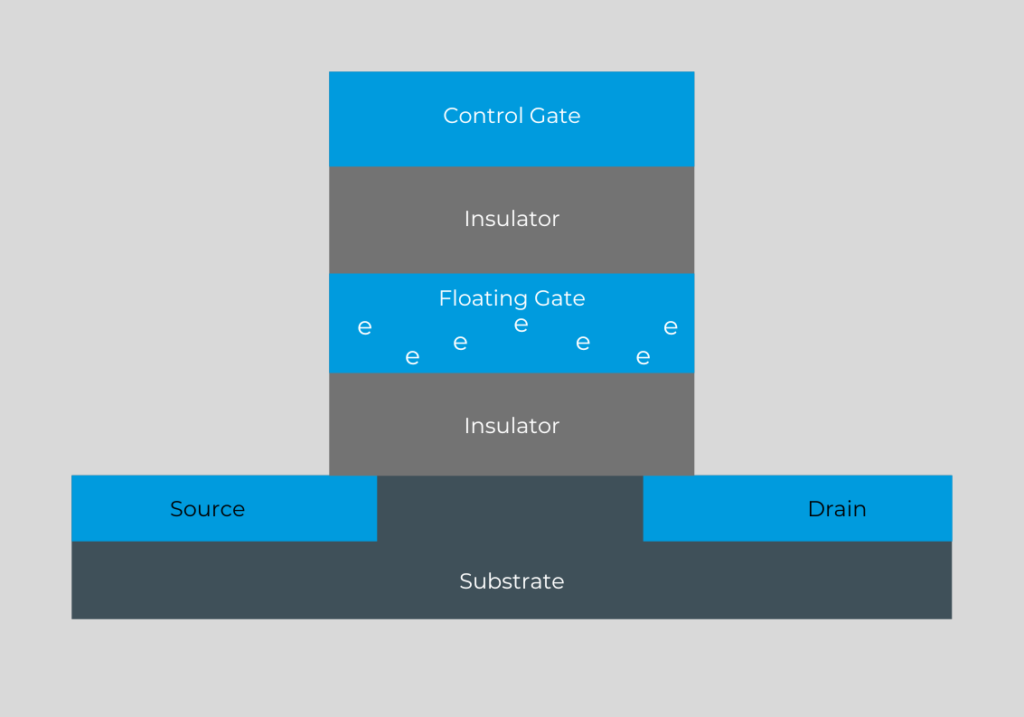

Um das Floating-Gate aufzuladen, wird eine hohe Spannung am Control-Gate angelegt, während der Abfluss und die Quelle geerdet sind. Elektronen bewegen sich vom Siliziumsubstrat (siehe obiges Diagramm) durch einen Effekt, der als Fowler-Nordheim-Tunnelling bekannt ist. Dort bleibt die Ladung auch dann erhalten, wenn am Control-Gate keine Spannung mehr anliegt. Man spricht deshalb von nichtflüchtigen Speicher.

Um die Zelle zu löschen, wird eine positive Spannung an das Siliziumsubstrat angelegt. Dies führt dazu, dass die Elektronen durch den unteren Isolator (im obigen Diagramm) zurücktunneln und das Floating-Gate nicht mehr geladen wird.

Beim Lesen der Speicherzelle muss festgestellt werden, ob das Floating-Gate geladen ist oder nicht. Um dies zu tun, ähnelt der Prozess der Art und Weise, wie ein üblicher Transistor als Schalter verwendet werden kann. Eine bekannte Spannung wird an das Steuer-Gatter angelegt (entlang der „Wordline“ in NAND, siehe später). Eine Spannung wird auch an den Abfluss (Drain) angelegt (diese Verbindung befindet sich entlang der „Bitline“ in NAND, siehe später) und der Abflussstromfluss wird mit einem Schwellenwert verglichen. Wenn der Drain-Strom über dem Schwellenwert liegt, bedeutet dies, dass das auf das Control-Gate angewendete Potential ausreichte, um den Transistor einzuschalten.

Da wir in Bezug auf die Ladung über eine analoge Größe sprechen, gibt es ein gewisses Maß an Unsicherheit – wo es schwer zu sagen ist, ob es definitiv eine 1 oder definitiv eine 0 darstellt. Es ist jedoch dieses analoge Verhalten, das es einer einzelnen Zelle ermöglicht, mehr als ein einzelnes Datenbit darzustellen – siehe später.

NAND-Flash-Zellen sind in Reihe geschaltet (Daisy-chained, drain to source). Der Abfluss der ersten Zelle ist über einen Standardtransistor (d. h. kein Floating-Gate) mit der Bitleitung verbunden, ebenso wie die Quelle der letzten Zelle mit der Quellleitung. NOR-Flash-Zellen werden parallel geschaltet, wobei der Abfluss jeder Zelle mit der Bitleitung und die Quelle mit der Quellleitung verbunden ist. Die folgenden beiden Diagramme zeigen die Unterschiede.

Oben ist die Reihen- (für NAND) und parallele (für NOR) Konnektivität zwischen Zellen dargestellt..

Es gibt Vor- und Nachteile, die mit beiden Verbindungsschemata verbunden sind. Zum Beispiel reduziert die Reihenschaltung in NAND die Anzahl der Erdungsdrähte und Bitleitungen – was sie zu einem sehr kompakten Speichertyp macht (d.h. weniger Chip-Platz und damit niedrigere Kosten), aber wir haben keinen direkten Zugriff auf einzelne Zellen, was den Speicherzugriff verlangsamt und den Verschleiß erhöht.

Im Gegensatz dazu sind in NOR die Transistoren parallel, so dass jeder Abfluss mit der Bitleitung und jede Quelle mit der Quellleitung verbunden ist, wodurch auf einzelne Zellen zugegriffen werden, kann. Dies ermöglicht einen schnelleren Zugang, aber es werden mehr Siliziumimmobilien benötigt, was die Kosten erhöht.

Als Speicherzelle (d.h. unabhängig davon, ob sie sich in NAND- oder NOR-Flash befindet) ist sie für 50.000 bis 100.000 Programm-/Löschzyklen geeignet – beide sind aufgrund der verwendeten Hochspannung „härter“ für die Zelle (als das Lesen). Die Transistoren verschleißen sich und die Floating-Gates brauchen länger zum Laden und Entladen.

Wie bereits erwähnt, verschleißt NAND aufgrund des fehlenden direkten Zugriffs auf einzelne Zellen schneller als NOR. Wenn sie jedoch in ein Speichergerät eingebettet sind (sei es eine SSD oder eine tragbare / austauschbare Karte oder ein Laufwerk), ist eine Verschleißnivellierungsschaltung (wear levelling circuitry) vorhanden.

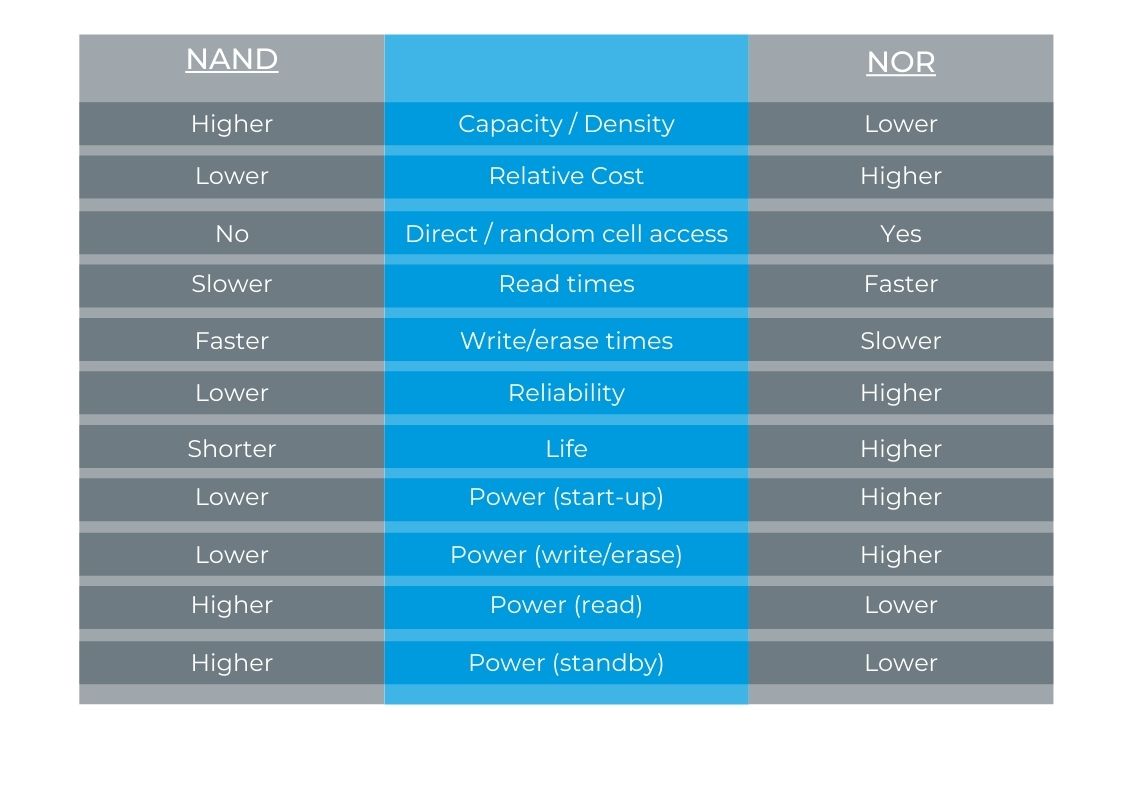

NAND versus NOR

Hier sind die Hauptunterschiede zwischen NAND und NOR.

Im Allgemeinen wird NAND tendenziell für die Datenspeicherung verwendet, insbesondere in kostengünstigen Konsumgütern (aber es gibt viele andere Anwendungen – siehe auch unsere Anleitung Wofür wird NAND-Speicher verwendet?). NOR hingegen wird tendenziell für die Speicherung und Ausführung von Programm / Code verwendet.

Wie die obige Tabelle zeigt, gibt es jedoch mehr Faktoren als nur Kapazität, Kosten und Geschwindigkeit, die bei der Auswahl eines Speichertyps berücksichtigt werden müssen. Wenn beispielsweise der Speicher in ein batteriebetriebenes Produkt integriert werden soll, muss der Stromverbrauch während des Startens, Schreibens, Löschens und Lesens (und im Standby-Modus) berücksichtigt werden. und all dies wird von den Funktionen des Produkts und den erwarteten Nutzungsgraden bestimmt.

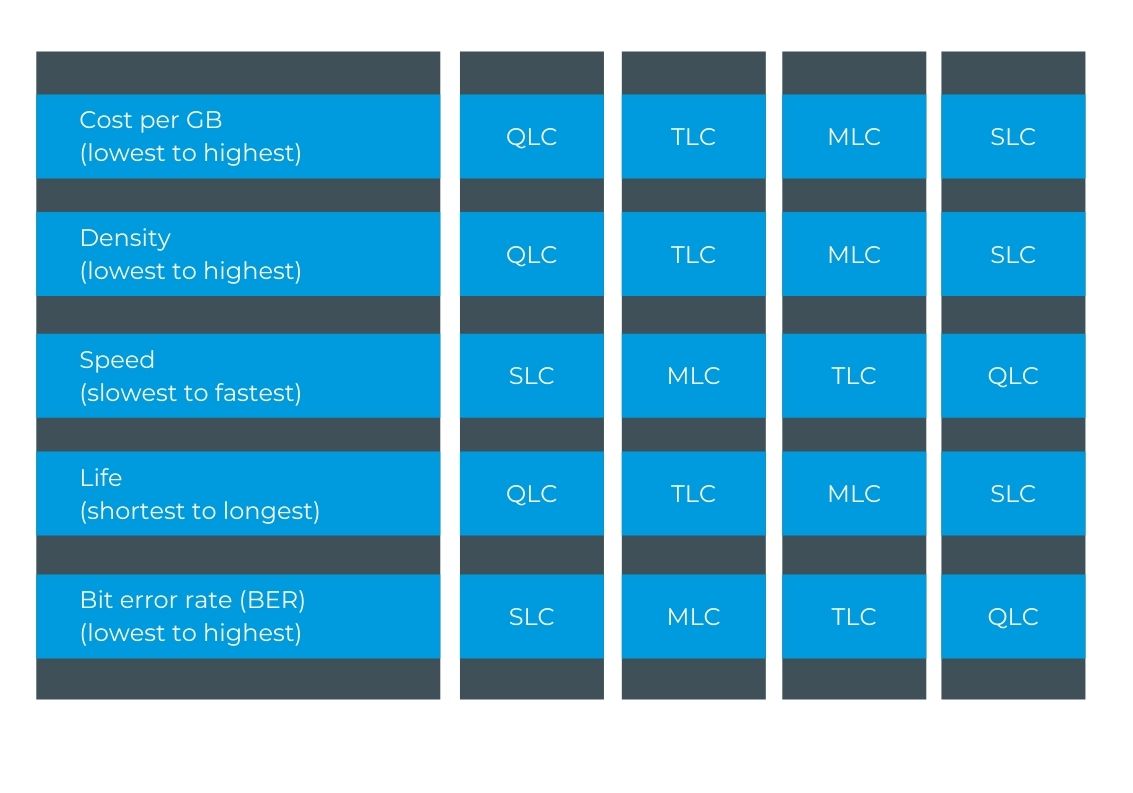

Bits pro NAND-Zelle

Oben haben wir erklärt, wie ein Floating-Gate-Transistor verwendet werden kann, um ein Bit Daten zu speichern. Dies wäre eine einzelne Ebenenzelle (Single Level Cell, SLC). Wie bereits erwähnt, werden die Daten als Ladung (eine analoge Größe) dargestellt, die mit einer Referenzspannung verglichen wird, um festzustellen, ob die Ladung eine 1 oder eine 0 darstellt.

Durch den Vergleich der Ladung mit mehr als einer einzigen Referenzspannung kann die Zelle verwendet werden, um mehr als ein einzelnes Datenbit darzustellen. Insbesondere, wenn:

- Es werden drei Referenzspannungen verwendet, die Zelle kann als vier mögliche Zustände betrachtet werden. Ausgedrückt als Zwei-Bit-Binärzahlen sind dies 00, 01, 10 und 11. Die Technik wird als Dual- oder Multilevel-Zelle (DLC oder MLC) bezeichnet.

- Die Verwendung von sieben Referenzspannungen ermöglicht die Darstellung von acht Drei-Bit-Zahlen (000 bis 111) und wird als Triple-Level-Zelle (TLC) bezeichnet.

- Die Verwendung von 15 Referenzspannungen ermöglicht die Darstellung von 16 Vier-Bit-Zahlen (0000 bis 1111) und wird als Quad-Level-Zelle (TLC) bezeichnet.

Die Hauptvorteile sind Speicher mit höherer Dichte/Kapazität. Es gibt jedoch Kompromisse, wie die folgende Tabelle zeigt.

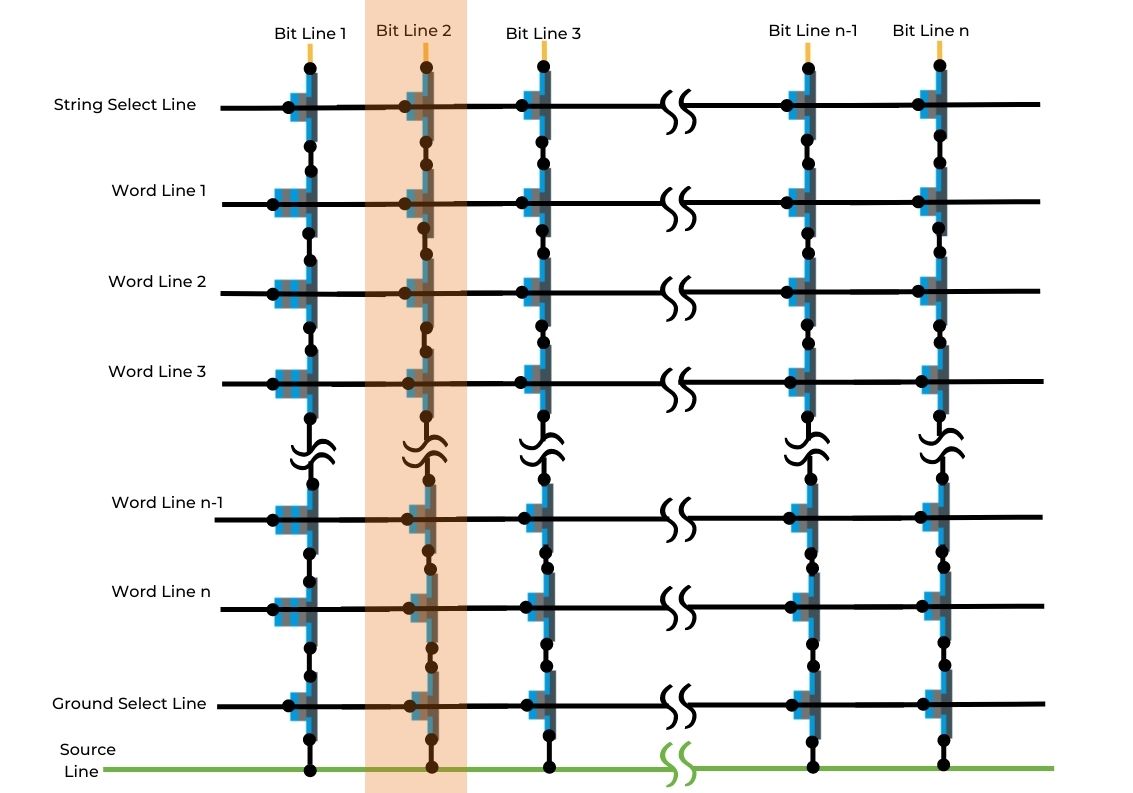

NAND-Flash-Speicherarchitektur

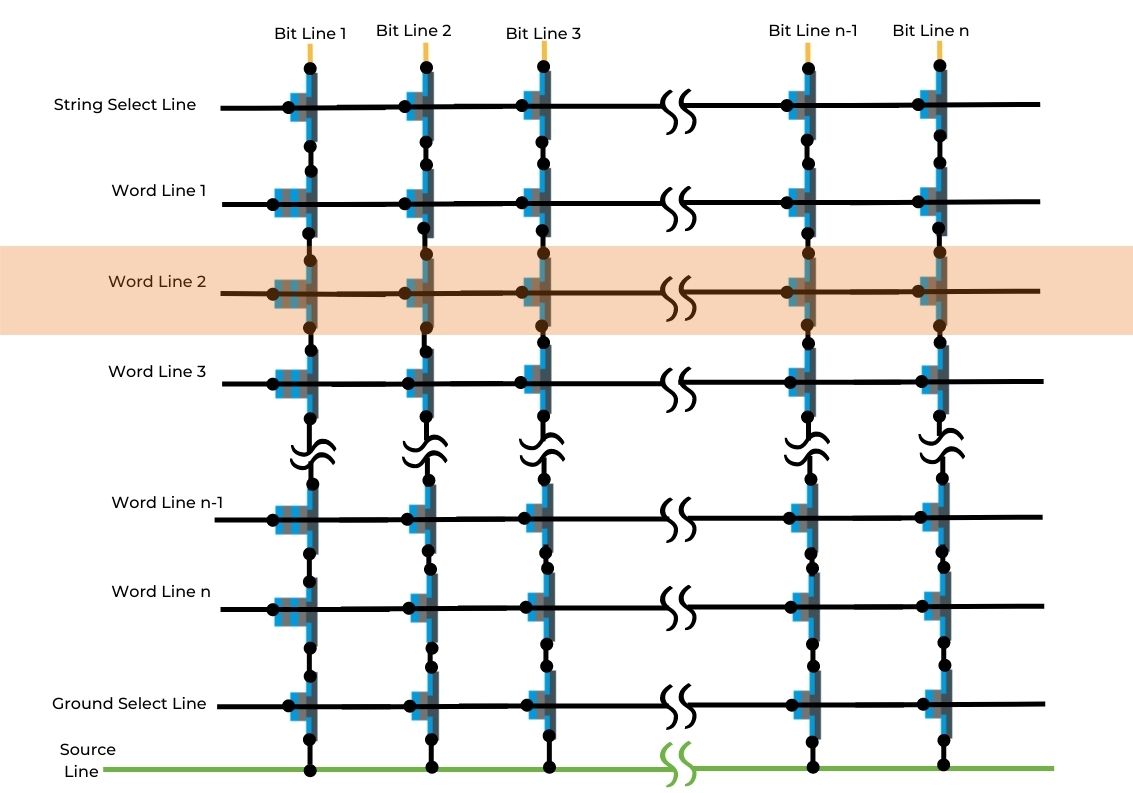

Ein NAND-Flash-Speicher (DIE) unterteilt sich in Ebenen und Blöcke. Ein Block ist effektiv ein Array (oder eine Matrix) von Zeichenfolgen (unten als Spalte hervorgehoben) und Pages (Zeilen von Zellen).

Oben besteht eine Zeichenfolge aus einer Reihe von Speicherzellen. Die Zeichenfolge für Bit Line ist hervorgehoben.

Eine Zeichenfolge ist das kleinste Volumen, das gelesen werden kann und in der Regel 32 oder 64 Zellen lang ist. Eine Seite besteht aus mehreren tausend Zellen, die die gleiche Wortzeile teilen. Die Seitengröße beträgt in der Regel 64 oder 128 KB.

Oben ist eine NAND-Seite eine Reihe von Zellen. Die Seite für Word-Zeile 2 ist hervorgehoben.

Ein 2 GB NAND-Speicher hat 2048 Blöcke mit 64 Seiten pro Block. Jede Seite enthält 2048 Bytes, die für die Datenspeicherung reserviert sind, plus 64 Bytes, die beispielsweise für die Fehlerkorrektur und den Verschleißnivellierung reserviert sind.

Schnittstellenbeschreibung

Die meisten Flash-Speicher verwenden das Common Flash Memory Interface (CFI), einen offenen Standard, der gemeinsam von AMD, Intel, Sharp und Fujitsu entwickelt und vom Unterausschuss für nichtflüchtige Speicher des Joint Electron Device Engineering Council (JEDEC) genehmigt wurde.

Flash-Speicher, der dem Standard entspricht, enthält Informationen über seine Kapazität, Konfiguration sowie Spannung und Timing.

JEDEC’s JESD68.01 kann hier heruntergeladen werden (Registrierung und Anmeldung erforderlich).